## Masterarbeit

zur Erlangung des akademischen Grades Master of Science (M.Sc.)

## Entwicklung und Implementierung der Hardware eines modularen Frequenzumrichters

Autor: Enes Darici

enes.darici@stud.hs-bochum.de Matrikelnummer: 018349551

Erstgutachter: Prof. Dr.-Ing. Arno Bergmann

Zweitgutachter: M.Sc. Sean William Dalton

**Abgabedatum:** 17.12.2023

## Eidesstattliche Erklärung

Eidesstattliche Erklärung zur Abschlussarbeit:

»Entwicklung und Implementierung der Hardware eines modularen Frequenzumrichters«

Ich versichere, die von mir vorgelegte Arbeit selbstständig verfasst zu haben. Alle Stellen, die wörtlich oder sinngemäß aus veröffentlichten oder nicht veröffentlichten Arbeiten anderer entnommen sind, habe ich als entnommen kenntlich gemacht. Sämtliche Quellen und Hilfsmittel, die ich für die Arbeit benutzt habe, sind angegeben. Die Arbeit hat mit gleichem Inhalt bzw. in wesentlichen Teilen noch keiner anderen Prüfungsbehörde vorgelegen.

Unterschrift: Ort, Datum:

Bochum, 17.12.2023

## Danksagung

Mein besonderer Dank gilt Prof.Dr.-Ing. Arno Bergmann und Sean William Dalton für ihre herausragende Betreuung und Unterstützung während meiner Masterarbeit.

Weiterhin gilt mein Dank auch Christoph Peters für die zusätzliche Unterstützung.

Die gemeinsam verbrachten Debug-Sitzungen waren nicht nur lehrreich, sondern auch äußerst produktiv.

Insbesondere bedanke ich mich bei meinem Mitstreiter Baris Akgül für die lehrund erlebnisreiche Zeit. Die Zusammenarbeit war nicht nur produktiv, sondern auch inspirierend.

## Inhaltsverzeichnis

| Inhaltsverzeichnis |                         |         |                                      | iii  |  |

|--------------------|-------------------------|---------|--------------------------------------|------|--|

| Αl                 | bkürz                   | ungsve  | erzeichnis                           | iv   |  |

| Sy                 | mbo                     | lverzei | chnis                                | vi   |  |

| 1                  | Einl                    | eitung  |                                      | 1    |  |

| 2                  | Theoretische Grundlagen |         |                                      |      |  |

|                    | 2.1                     | Mikro   | ocontroller                          | . 3  |  |

|                    | 2.2                     | Signa   | lintegrität                          | . 4  |  |

|                    |                         | 2.2.1   | differenzielle Signalübertragung     |      |  |

|                    |                         | 2.2.2   | Signalimpedanzen                     |      |  |

| 3                  | Anf                     | orderu  | ngserhebung                          | 7    |  |

|                    | 3.1                     | Umfel   | ldmodellierung                       | . 8  |  |

|                    | 3.2                     | Anwe    | ndungsszenarien                      | . 9  |  |

|                    | 3.3                     | Anfor   | derungsdokumente                     | . 9  |  |

|                    | 3.4                     | Wirks   | strukturen                           | . 9  |  |

| 4                  | Sys                     | tement  | twurf                                | 14   |  |

|                    | 4.1                     | Lösun   | ngsarchitekturen                     | . 14 |  |

|                    | 4.2                     | Komp    | ponentenentwurf                      | . 18 |  |

|                    |                         | 4.2.1   | Schaltregler                         | . 18 |  |

|                    |                         | 4.2.2   | Mikrocontroller                      | . 20 |  |

|                    |                         | 4.2.3   | USB/UART-Schnittstelle               | . 21 |  |

|                    |                         | 4.2.4   | Ethernet                             | . 21 |  |

|                    |                         | 4.2.5   | Verpolungsschutz/Überspannungsschutz |      |  |

|                    |                         | 4.2.6   | Leistungsstufe                       |      |  |

### In halts verzeichn is

| 5  | lmp   | plementierung                                            |  |  | 25  |  |

|----|-------|----------------------------------------------------------|--|--|-----|--|

|    | 5.1   | Schaltregler                                             |  |  | 27  |  |

|    |       | 5.1.1 Dimensionierung 3,3 V-Ebene                        |  |  | 27  |  |

|    |       | 5.1.2 Schaltplan und Layout                              |  |  | 28  |  |

|    |       | 5.1.3 Dimensionierung $1,2 \text{ V-Ebene}$              |  |  | 30  |  |

|    |       | 5.1.4 Schaltplan und Layout                              |  |  | 30  |  |

|    | 5.2   | Mikrocontroller                                          |  |  | 32  |  |

|    |       | 5.2.1 Schaltplan                                         |  |  | 32  |  |

|    |       | 5.2.2 Layout                                             |  |  | 35  |  |

|    | 5.3   | USB/UART-Schnittstelle                                   |  |  | 36  |  |

|    |       | 5.3.1 Schaltplan                                         |  |  | 36  |  |

|    |       | 5.3.2 Layout                                             |  |  | 38  |  |

|    | 5.4   | Ethernet                                                 |  |  | 39  |  |

|    |       | 5.4.1 Schaltplan                                         |  |  | 39  |  |

|    |       | 5.4.2 Layout                                             |  |  | 40  |  |

|    | 5.5   | Verpolungsschutz/ $\ddot{\mathrm{U}}$ berspannungsschutz |  |  | 41  |  |

|    |       | 5.5.1 Dimensionierung                                    |  |  | 41  |  |

|    |       | 5.5.2 Schaltplan                                         |  |  | 42  |  |

|    |       | 5.5.3 Layout                                             |  |  | 43  |  |

|    | 5.6   | 5.6 Leistungsstufe/GPIOs                                 |  |  |     |  |

|    |       | 5.6.1 Schaltplan                                         |  |  | 44  |  |

|    |       | 5.6.2 Layout                                             |  |  | 45  |  |

|    | 5.7   | Frequenzumrichter                                        |  |  | 47  |  |

| 6  | Veri  | rifikation                                               |  |  | 48  |  |

|    | 6.1   | Versorgungspfad                                          |  |  | 49  |  |

|    | 6.2   | Kommunikationspfad: Mikrocontroller                      |  |  | 52  |  |

|    | 6.3   | Kommunikationspfad: Ethernet                             |  |  | 54  |  |

|    | 6.4   | Integrationstest: Frequenzumrichter                      |  |  | 55  |  |

| 7  | Fazi  | zit und Ausblick                                         |  |  | 57  |  |

| Αŀ | bildı | dungsverzeichnis                                         |  |  | 11  |  |

| Ta | helle | lenverzeichnis                                           |  |  | 111 |  |

### In halts verzeichn is

| Lit | eratur     |   | IV   |

|-----|------------|---|------|

| Α   | Anhang     | , | VIII |

|     | A.1 Inhalt |   | VIII |

## Abkürzungsverzeichnis

ADC Analog Digital Converter

**BGA** Ball Grid Array

**CAN** Controller Area Network

CONSENS CONceptual design Specification technique for the Engineering of

${\it complex Systems}$

**CSA** Current Shunt Amplifier

eCAP Enhanced Capture Mode

**EEPROM** Electrically Erasable Programmable Read Only Memory

**EpOS** Entwicklungsplattform-Ortsfrequenzfilter-Sensor

ePWM Enhanced Pulse Width Modulator

**ESD** Electro Static Discharge

FTDI Future Technology Devices International

**GPIO** General Purpose Input/Output

**HIL** Hardware in the Loop

IC Integrated Circuit

JTAG Joint Venture Action Group

**QFP** Quad Flat Package

SMI Serial Management Interface

#### In halts verzeichn is

${f TCP/IP}$  Transmission Control Protocol/Internet Protocol

TI Texas Instruments

**UART** Universal Asynchronous Receiver Transmitter

**USB** Universal Serial Bus

# Symbolverzeichnis

| Symbol        | Bedeutung               | Einheit       |

|---------------|-------------------------|---------------|

| C             | elektrische Kapazität   | F             |

| $C_{OUT}$     | Ausgangs-Kapazität      | F             |

| $C_L$         | Last-Kapazität          | F             |

| $f_{\sf sw}$  | ${\bf Schaltfrequenz}$  | $\mathrm{Hz}$ |

| $I_{\sf max}$ | Maximal-Strom           | A             |

| L             | Induktivität            | Н             |

| R             | elektrischer Widerstand | $\Omega$      |

| $V_{OUT}$     | Ausgangs-Spannung       | V             |

| $V_{IN}$      | Eingangs-Spannung       | V             |

| $V_{OV}$      | Über-Spannung           | V             |

| $V_{\sf UV}$  | Unter-Spannung          | V             |

## 1 Einleitung

Die vorliegende Arbeit befasst sich mit der Dokumentation der Hardware-Entwicklung eines modularen Frequenzumrichters und wurde am Institut für Systemtechnik in Zusammenarbeit mit der Smart Mechatronics GmbH durchgeführt.

Die Grundlage für die mittlerweile dritte Generation des Frequenzumrichters am Institut für Systemtechnik, stellt zum einen die im "HoBo" -E-Skateboard-Projekt entwickelte Leistungselektronik und zum anderen die Hardware-Entwicklung im EpOS-Projekt dar [1, 2].

Zuvor wurde innerhalb einer Projektarbeit, auf der Basis einer Beispielapplikation eines Cargo-Pedelecs, die Anforderungserhebung entwickelt, um die Rahmenbedingungen für diese Arbeit festzulegen [3].

Die Bearbeitung der Abschlussarbeit läuft zeitgleich und in gegenseitiger Abhängigkeit zur Arbeit "Modellbasierte Entwicklung und Verifikation mit MATLAB/Simulink eines modularen Frequenzumrichters" von Baris Akgül [4].

## 2 Theoretische Grundlagen

In diesem Kapitel werden die theoretischen Grundlagen für die Entwicklung eines Frequenzumrichters beschrieben.

Dabei wird der Fokus auf einige zentrale Aspekte im Bereich des Schaltplanund Layoutentwurfs gerichtet, um den Umfang dieses Kapitels in angemessenem Rahmen zu halten:

#### • Mikrocontroller:

Der Mikrocontroller stellt einen zentralen Bestandteil für die Ansteuerung einer Synchronmaschine dar und ist eine entscheidende Komponente, die während des Entwicklungsprozesses besonders im Layoutentwurf bestimmte Anforderungen erfüllen muss, um eine zuverlässige Anwendung zu gewährleisten [5, 6].

#### • Signalintegrität:

Die Signalintegrität ist ein fester Bestandteil im Layout und Routing. Das Ziel dabei ist, dass sich die Qualität eines Signals bei der Übertragung von einer Quelle zu einer Senke nicht verschlechtert [6, 7].

Die im Verlauf dieses Projektes verwendeten zusätzlichen Grundlagen, sind entsprechend gekennzeichnet und können im Literaturverzeichnis eingesehen werden.

#### 2.1 Mikrocontroller

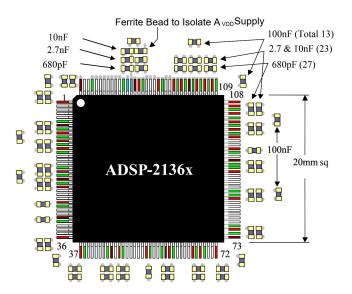

Eine zuverlässige Versorgungsspannung bildet die Grundlage für die korrekte Anwendung eines Mikrocontrollers, da die Leistungsaufnahme sich kontinuierlich ändert [6]. Oftmals sind repräsentative Leistungsaufnahmen innerhalb der Datenblätter vorgegeben und werden als Annäherung genutzt, da die Leistungsauforderungen sich nach Anwendung und Konfigurationsdichte innerhalb des Mikrocontrollers variieren [8].

Je nach Anwendung können Spitzenströme innerhalb der Versorgungsleitung entstehen, die von der Spannungsquelle bereitgestellt werden müssen. Eine simple Leitung von der Quelle zur Senke ist in den meisten Fällen nicht ausreichend um die Stromspitzen zu übertragen, da die parasitären Elemente innerhalb der Versorgungsleitungen die Fähigkeit der Leiterbahnen beeinträchtigen [6].

Abhilfe schaffen in diesem Fall sogenannte Bypass-Kondensatoren, die als Energiereservoir dienen, um kurzfristige Stromspitzen bereitzustellen [6]. Die genaue Anzahl und Werte sind in den meisten Fällen innerhalb der Datenblätter angegeben [8].

Platziert werden die Bypass-Kondensatoren dabei so nah wie möglich am jeweiligen IC-Pin, um die parasitären Charakteristiken innerhalb der Leitungen so klein wie möglich zu halten.

Eine beispielhafte Platzierung an einem QFP-Gehäusetyp ist in der Abbildung 2.1 dargestellt.

Bei mehreren Kondensatoren an einem Pin, wird nach Kapazitätswert geordnet. Dabei wird der kleinere Wert näher am Versorgungsanschluss platziert. Des Weiteren muss sichergestellt werden, dass der Strom zuerst den Bypass-Kondensator passiert und dann in die Versorgungspins fließt [5].

Abbildung 2.1: Beispielhafte Platzierung von Bypass-Kondensatoren an einem QFP-Gehäuse [5]

### 2.2 Signalintegrität

#### 2.2.1 differenzielle Signalübertragung

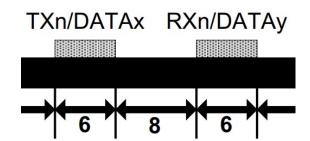

Die Verwendung der differenziellen Signalübertragung hat sich aufgrund ihrer hohen Störfestigkeit als Grundlage beim Entwurf von High-Speed Signalübertragungen etabliert. Dabei werden gemeinsame Störsignale, die beide Signalleitungen gleichzeitig beeinflussen, eliminiert [6].

Eine differenzielle Übertragung besteht aus zwei Leiterbahnen sowie einer Massefläche als Referenz für die Rückführung der Ströme [9].

In der Abbildung 2.2 wird eine beispielhafte Anwendung einer differenziellen Signalübertragung dargestellt.

Innerhalb der Übertragung müssen bestimmte Anforderungen eingehalten werden, um eine zuverlässige Signalintegrität zu gewährleisten. Oftmals werden diese innerhalb der Datenblätter bereitgestellt [10].

Zwei wesentliche Anforderungen sind:

#### • Leiterbahnbreite:

Bezieht sich immer auf beide Leitungen innerhalb der Signalübertragung und wird in Abhängigkeit der geforderten Signalimpedanz bestimmt.

#### • Leiterbahnabstand:

Ist sowohl der Abstand zwischen den beiden differenziellen Signale als auch der zu angrenzenden Leitungen.

Abbildung 2.2: Beispielhafte Anwendung einer differenziellen Signalübertragung [11]

### 2.2.2 Signalimpedanzen

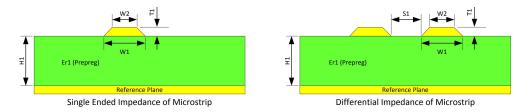

Bei der Signalimpedanz unterscheidet man zwischen sogenannten single-ended und differenziellen Signalen [6].

Die Impedanz bezieht sich dabei zwischen der Signalleitung und ihrer Referenzfläche, oftmals in Leiterplatten als Massefläche gekennzeichnet. Die Abbildung 2.3 stellt eine beispielhafte Leitungsgeometrie sowohl für eine single-ended als auch eine differenzielle Signalführung dar.

Abbildung 2.3: Beispielhafte Leitungsgeometrien für Signalimpedanzen an singleended und differenziellen Signalen [6]

Eine Signalimpedanz ist oftmals in den Datenblättern vorgegeben und muss eingehalten werden, um eine zuverlässige Signalintegrität zu gewährleisten. Bei Nichtbeachtung kann Crosstalk oder die Reflektion des übertragenen Signals entstehen [7].

Um die Impedanz anzupassen, können mehrere Parameter angepasst werden. Zum einen ist es die Leiterbahnbreite  $W_1$  als auch die Leiterbahnhöhe  $T_1$ . Des Weiteren kann der Abstand zur Referenzfläche  $H_1$  und zum anderen der Abstand zwischen den Leitungen  $S_1$  bei differenzieller Signalübertragung verändert werden, um die gewünschte Impedanz zu erhalten.

Die Festlegung der Impedanzen werden standardmäßig vor dem ersten Layoutentwurf getroffen, um die gewünschte Leiterplatte mit den geeigneten Signaleigenschaften zu bestimmen. Oftmals ist eine Rücksprache mit dem Leiterplattenentwickler sinnvoll, um sicherzustellen, dass die gewünschte Leiterplatte produzierbar ist [6].

## 3 Anforderungserhebung

In diesem Kapitel werden die Rahmenbedingungen zum Projekt festgelegt. Die sogenannte Anforderungserhebung.

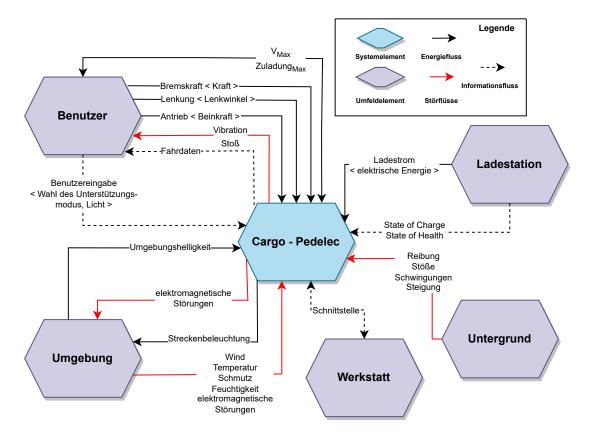

Die Anforderungen werden mit Hilfe der CONSENS®-Methode erhoben [12]. Diese Methode ist eine Spezifikationstechnik zur Entwicklung von Systemarchitekturen über ein Umfeldmodell.

Auf eine detaillierte Beschreibung der Methode wird verzichtet, da sie bereits in vorangegangenen Projekten am Institut für Systemtechnik ausführlich dokumentiert und angewendet wurde [12, 13].

Die Ergebnisse der CONSENS®-Methode werden in der folgenden Reihenfolge erarbeitet:

- Umfeldmodellierung

- Anwendungsszenarien

- Anforderungsdokumente

- Wirkstrukturen

## 3.1 Umfeldmodellierung

Zunächst wird das Systemumfeld definiert und die Schnittstellen zwischen System und Umfeld entwickelt [12].

Das Umfeldmodell für den Anwendungsfall des Cargo-Pedelecs ist in Abbildung 3.1 dargestellt.

Das Cargo-Pedelec wird als Systemelement eingetragen und über unterschiedliche Pfeile mit den jeweiligen Umfeldelementen verknüpft. Die Pfeile stellen hierbei die Schnittstelle im Systemumfeld dar. Dabei wird zwischen Energie-, Informations-, und Störeinflüssen unterschieden.

Abbildung 3.1: Umfeldmodell Cargo-Pedelec

## 3.2 Anwendungsszenarien

Auf Grundlage der Umfeldanalyse werden die Anwendungsszenarien definiert. Dieser Prozess beinhaltet die Beschreibung verschiedener Szenarien in Zusammenhang mit dem gewünschten Verhalten innerhalb dieser Szenarien [12].

Die definierten Anwendungsszenarien des Cargo-Pedelecs sind dieser Arbeit angehängt (siehe Anhang A.1.3).

### 3.3 Anforderungsdokumente

Auf der Basis von Umfeldmodell und Anwendungsszenarien werden die Anforderungen an das System in einem Lastenheft festgehalten.

Für eine ausführliche Beschreibung des Lastenhefts wird auf die Masterarbeit, am Institut für Systemtechnik, von Florian Wagner verwiesen [13].

Die im Zuge dieses Projektes entstandenen Anforderungen sind dieser Arbeit angehängt (siehe Anhang A.1.2).

#### 3.4 Wirkstrukturen

In diesem Abschnitt wird die Wirkstruktur für die Elektronik des Cargo-Pedelecs sowie die Wirkstruktur für den Frequenzumrichter dargestellt. Außerdem werden die Spannungsebenen am Frequenzumrichter definiert und ein Blockschaltbild für das Gesamtsystem erstellt.

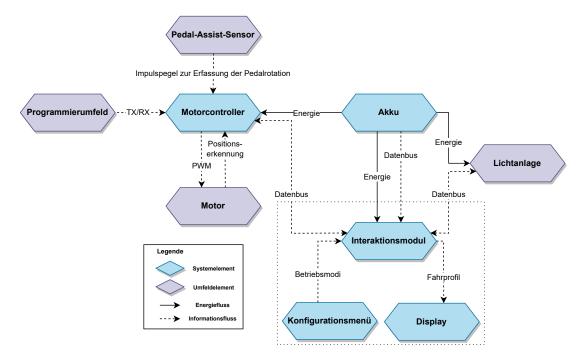

Die Wirkstruktur für die Elektronik des Cargo-Pedelecs wird in der Abbildung 3.2 dargestellt.

Laut Lastenheft (siehe Anhang A.1.2) soll ein Motor angesteuert und geregelt werden. Um das zu gewährleisten wird ein Motorcontroller eingesetzt. Außerdem wird ein Interaktionsmodul verwendet, um eine Kommunikation mit dem Fahrer zu ermöglichen. Um die Interaktion zu gewährleisten, wird eine Datenbus-Schnittstelle eingesetzt.

Weitere Umfeldelemente der Elektronik sind das Programmierumfeld zur Softwareanpassung, eine Lichtanlage am Fahrrad sowie ein sogenannter Pedal-Assist-Sensor zur Erfassung der Impulse an der Tretkurbel, um das Einschalten des Elektroantriebs zu ermöglichen [14].

Abbildung 3.2: Wirkstruktur Elektronik

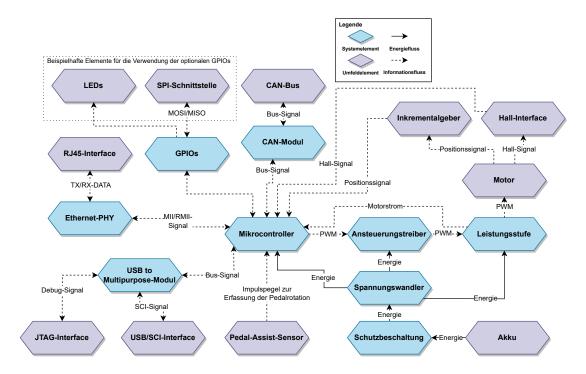

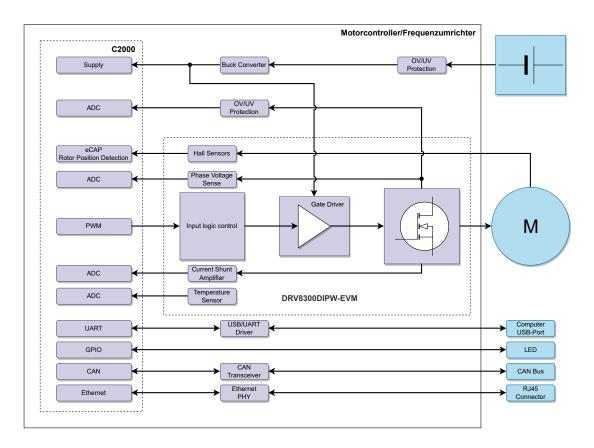

Die Abbildung 3.3 zeigt die Wirkstruktur des Motorcontrollers. Als Systemelemente sind die im Motorcontroller implementierten Architekturen abgebildet. Die Umfeldelemente sind als Interaktion zu den Systemelementen über die jeweiligen Schnittstelle dargestellt.

Abbildung 3.3: Wirkstruktur Motorcontroller/Frequenzumrichter

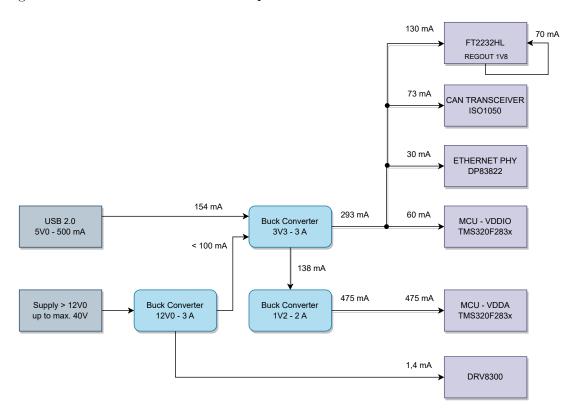

Auf Grundlage der entwickelten Wirkstrukturen sind die Komponenten in Abhängigkeit ihrer definierten Spannungsebenen in der Abbildung 3.4 dargestellt.

Abbildung 3.4: Komponenten des Motorcontrollers und die dazugehörigen Spannungsebenen

Die Spannungsebenen werden im Laufe des Systementwurfs benötigt, um die im Abschnitt 4.1 vorgestellten Konzepte zur Versorgung des Frequenzumrichter zu erstellen.

Außerdem werden auf Grundlage der Spannungsebenen die im Abschnitt 4.2 beschriebenen Schaltregler ausgehend von der Leistungsaufnahme der Komponenten dimensioniert.

Den Abschluss der Anforderungserhebung stellt das Blockschaltbild des Gesamtsystems in der Abbildung 3.5 dar.

Abbildung 3.5: Blockschaltbild Gesamtsystem

Auf Grundlage dieses Blockschaltbilds wird das Lastenheft für den Frequenzumrichter entworfen (Siehe Anhang A.1.1).

Aus den abgeleiteten Anforderungen werden im Anschluss an die Implementierung, die Verifikationen an der entwickelten Hardware durchgeführt.

## 4 Systementwurf

In diesem Kapitel erfolgt die Konzeption des Systementwurfs im Rahmen der zuvor festgelegten Anforderungen gemäß Kapitel 3.

Darüber hinaus werden die Hauptkomponenten des Frequenzumrichters definiert.

### 4.1 Lösungsarchitekturen

Zu Beginn werden Lösungsarchitekturen mit Hilfe eines morphologischen Kastens aufgeführt. Dies ermöglicht eine Betrachtung potenzieller Lösungsarchitekturen [15].

Ein Teil wird in der Tabelle 4.1 aufgelistet, samt gewählter Lösungen dargestellt und im Anschluss beschrieben.

| Parameter                     | Lösungsarchitekture | $\mathbf{n}$             |                  |

|-------------------------------|---------------------|--------------------------|------------------|

| Mikrocontroller               | ControlCard         | Layout                   |                  |

| ${ m Leistungs stufe}$        | DRV8300DIPW-EVM     | Layout                   |                  |

| $\operatorname{Schaltregler}$ | integriert          | $\operatorname{diskret}$ |                  |

| Motorpositionserkennung       | Hall-Sensor         | Sensorlos                | Inkrementalgeber |

| Lagenzahl                     | 2                   | 4                        | 6                |

Tabelle 4.1: Parameter mit möglichen Lösungsarchitekturen und gewählte Lösung

Aufgrund der erfolgreichen Anwendung in bereits abgeschlossenen Projektarbeiten, wird die Anforderung zur Verwendung eines Mikrocontrollers der

C2000-Reihe von Texas Instruments (TI) im Lastenheft festgelegt (Anhang

A.1.1) [2, 8, 13]. Entsprechend dieser Vorgabe wird von der Nutzung einer sogenannten controlCARD abgesehen [24]. Die Implementierung einer ControlCARD

beschränkt die Funktionen des Mikrocontrollers, da der Entwickler nicht alle

verfügbaren Funktionen, aufgrund von begrenztem Bauraum, implementieren

kann. Um die Bandbreite an Funktionen zu nutzen, wird der Mikrocontroller auf die eigens entwickelte Hardware des modularen Frequenzumrichters verbaut. Die Auswahl des Mikrocontrollers wird in Abschnitt 4.2.2 detailliert beschrieben.

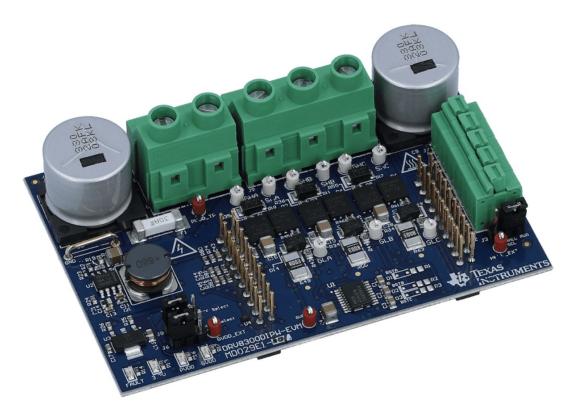

Entsprechend des Projektumfangs, wird auf die Implementierung einer eigenen Leistungsstufe auf die Hardware verzichtet. Eine Vorgabe vom Auftraggeber ist die Beschaffung dieser. Als gewählte Leistungsstufe wird der DRV8300DIPW-EVM von TI verwendet [16]. Auf dem Frequenzumrichter werden entsprechende Anschlüsse vorgesehen, um die Leistungsstufe anzuschließen.

Die Schnittstelle erlaubt eine Erweiterung auf künftige, an die jeweilige Anwendung angepasste Leistungsstufen.

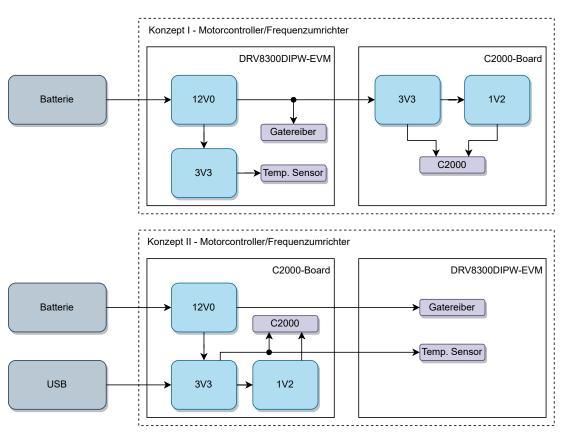

In diesem Projekt können zum Einen die integrierten Schaltregler der Leistungsstufe verwendet werden, zum Anderen diskrete Schaltregler welche im Design des modularen Frequenzumrichters beinhaltet sind. Im Zuge dieser alternativen Lösungsarchitekturen werden in der Abbildung 4.1 diese zwei Konzepte miteinander verglichen.

Die Auswahl der Schaltregler wird im Abschnitt 4.2.1 detailliert beschrieben.

Die Konzepte zur Versorgung des Frequenzumrichters werden anhand der entwickelten Spannungsebenen gemäß Abbildung 3.4 erstellt.

Abbildung 4.1: Vergleich der Konzepte zur Versorgung des Frequenzumrichters

Im Folgenden werden die Konzepte vorgestellt:

#### • Konzept I:

Die bestehenden Schaltregler auf der Leistungsstufe können in Kombination mit zusätzlichen Schaltreglern auf dem Frequenzumrichter genutzt werden, was eine raumsparende Lösung für die zu entwickelnde Hardware ermöglicht.

Die Integration führt jedoch zu einer Abhängigkeit, da die Versorgung des C2000 nun von der Leistungsstufe abhängig ist. Infolgedessen wird der Betrieb des Mikrocontrollers ohne die Leistungsstufe nicht möglich.

#### • Konzept II:

Die Versorgung des C2000 und der Leistungsstufe werden vollständig auf die zu entwickelnde Hardware verlegt. Zudem wird die im Lastenheft (Anhang A.1.1) geforderte Versorgung durch eine USB-Schnittstelle implementiert. Dies gewährleistet die vom Auftraggeber geforderte Nutzung des Frequenzumrichters ohne eine Leistungsstufe. Dazu müssen geeignete Schaltregler in Abhängigkeit der von den Komponenten benötigten Stromaufnahme bestimmt werden.

Entsprechend den spezifizierten Anforderungen im Lastenheft wird die Entscheidung zugunsten des zweiten Konzepts getroffen.

Zur Motorpositionserkennung sind sowohl ein Hall-Sensor-Interface als auch ein Inkrementalgeber implementiert. Der Inkrementalgeber dient als eine redundante Datenquelle für die Positionsbestimmung, wird im Rahmen dieser Abschlussarbeit jedoch nicht verifiziert. Es ermöglicht eine projektübergreifende Anwendung des Frequenzumrichters.

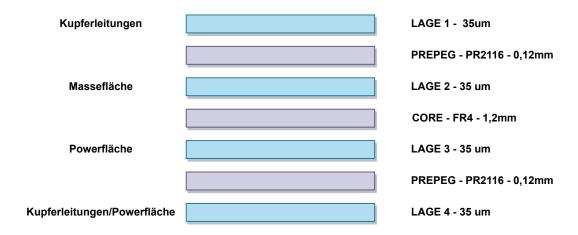

Der Lagenaufbau ist unter Berücksichtigung der Positionierung der Komponenten auf der Leiterplatte ermittelt. In Anbetracht einer zuverlässigen Signalintegrität sowie dem Kompromiss zwischen Komplexität und Kosten ist die Entscheidung auf eine Leiterplatine mit 4 Lagen gefallen.

### 4.2 Komponentenentwurf

In diesem Kapitel werden die ausgewählten Hauptkomponenten im Rahmen des Systementwurfs näher erläutert. Dies beinhaltet eine detaillierte Beschreibung dieser Komponenten und der jeweiligen Funktionen.

Die Hauptkomponenten werden in folgender Reihenfolge beschrieben:

- Schaltregler (12 V, 3,3 V, 1.2 V)

- Mikrocontroller

- USB/UART-Schnittstelle (inklusive JTAG-Schnittstelle)

- Ethernet

- Verpolungsschutz/Überspannungsschutz

- Leistungsstufe (Stiftleisten zur Kontaktierung)

#### 4.2.1 Schaltregler

Die Grundlage für die Auswahl der Schaltregler stellt die Abbildung 3.4 dar. Die Spannungsebenen und ihre Verbraucher werden definiert, um im Anschluss den benötigten Strom zu bestimmen.

Die benötigten Spannungen werden mit drei Schaltreglern realisiert. Sowohl für die 12 V-Ebene als auch für die 3,3 V-Ebene wird der Schaltregler LT8609 von Analog Devices ausgewählt [17]. Dieser hat sich bereits in der vorangegangenen Projektarbeit EpOS bewährt und wurde vom Auftraggeber empfohlen [2, 13]. Für die Wandlung von 3,3 V auf 1,2 V wird der Schaltregler LT3302 verwendet [18].

Des Weiteren wird der benötigte Strom bestimmt, um die Eingangs- und Ausgangsströme der Schaltregler zu identifizieren. Die Abbildung 4.2 stellt die Verbraucher und ihre Stromaufnahme dar. Der Stromverbrauch wurde aus den entsprechenden Datenblättern entnommen. Sicherheitshalber werden für die Rechnung der Eingangsströme am Schaltregler ein Wirkungsgrad von 80 % berücksichtigt.

Neben der Versorgung durch eine USB-Schnittstelle sollen laut Lastenheft weitere Spannungseingänge den Frequenzumrichter versorgen können. Diese Möglichkeit wird in der Abbildung 4.2 zusätzlich dargestellt. Dabei werden Spannungseingänge oberhalb von 12 V bis 40 V akzeptiert.

Abbildung 4.2: Eingangs- und Ausgangsströme der Schaltregler und Verbraucher

Die Stromaufnahme auf der  $12\,\mathrm{V}$ -Ebene setzt sich aus dem Eingangsstrom für den  $3,3\,\mathrm{V}$  Schaltregler sowie dem Versorgungsstrom des Gatetreibers auf der DRV8300DIPW-EVM Leistungsstufe zusammen.

Der LT8609 Schaltregler weist einen großen Eingangsspannungsbereich von 3,0 V bis 42 V vor. Dadurch wird eine Versorgung der 3,3 V-Ebene sowohl mit 5 V durch die USB-Schnittstelle als auch mit 12 V aus dem Schaltregler gewährleistet. Um sicherzustellen, dass die Hardware bei gleichzeitigem Anschluss beider Versorgungsquellen einwandfrei funktioniert, wird das sogenannte ORing-Verfahren genutzt. Dazu werden zwei Schottky-Diode jeweils am Eingang des 3,3 V Schaltreglers eingesetzt [20].

Die Stromaufnahme auf der 1.2 V-Ebene ist ausschließlich durch den Mikrocontroller gegeben. Der LTC3302, mit einer maximalen Schaltfrequenz von 6 MHz, kann einen Strom von 2 A bei einer maximalen Eingangsspannung von 5.5 V liefern [18].

Die Implementierung der Schaltregler wird im Abschnitt 5.1 detailliert beschrieben.

#### 4.2.2 Mikrocontroller

Bereits in den vorangegangen Projekten wurde die Auswahl des Mikrocontrollers im Kontext der Motoransteuerung ausführlich erläutert [2, 13].

Der Fokus liegt hier vielmehr auf den zusätzlichen Anforderungen, die im Zuge dieses Projekts erhoben wurden.

Grundsätzlich werden folgende Peripherien zur Ansteuerung einer Synchronmaschine mit Hallsensorik benötigt [13]:

- CAP-Module

- PWM-Mdoule

- ADC-Module

Darüber hinaus werden folgende Peripherien im Lastenheft gefordert:

- Ethernet

- CAN-Bus

Die Ethernet-Schnittstelle ermöglicht über das sogenannte Transmission Control Protocol/Internet Protocol (TCP/IP-Protokoll) Echtzeitkommunikationen innerhalb der Simulink-Toolkette [21]. Weiterhin werden sogenannte Hardware in the Loop (HIL)-Simulationen möglich [22].

Die Implementierung und Anwendung wird in der zeitgleich entwickelten Arbeit ausführlich erläutert [4].

Als Kommunikationsschnittstelle wird eine CAN-Bus Schnittstelle implementiert, da diese sich als störsicheres Bussystem zur Kommunikation mit anderen Modulen eignet [2].

Ein TI C2000-Mikrocontroller mit dafür ausreichender Peripherie ist der F28386D. Dieser verfügt über 32 ePWM-Module und 7 eCAP-Module. Weiterhin verfügt es über 4 ADC-Module sowie über eine Ethernet-Schnittstelle [8].

Aufgrund der prozesssicheren Anwendung, in Bezug auf das Löten und Entlöten, wird der Mikrocontroller im QFP-Gehäuse eingesetzt.

#### 4.2.3 USB/UART-Schnittstelle

Als USB/UART-Schnittstelle wird der FT2232HL von dem Unternehmen Future Technology Devices Internatinal (FTDI) eingesetzt [23]. Diese Schnittstelle ermöglicht die Kommunikation zum Computer und damit auch zur Software. Es entspricht von der Architektur dem in der controlCARD TMDSCNCD28388D eingesetzten Variante [24].

Der FT2232HL verfügt über zwei Kanäle, die unabhängig voneinander konfiguriert werden können. Deshalb wird ein Joint Test Action Group (JTAG) Protokoll zusätzlich implementiert, um das Testen und Debuggen integrierter Schaltungen zu ermöglichen [25].

#### 4.2.4 Ethernet

Laut Lastenheft (Anhang A.1.1) soll die Ethernet-Schnittstelle aus der control-CARD TMDSCNCD28388D implementiert werden. Dabei wird der DP83822 von TI eingesetzt [10].

Die Implementierung der Ethernet-Schnittstelle wird im Abschnitt 5.4 detailliert beschrieben.

#### 4.2.5 Verpolungsschutz/Überspannungsschutz

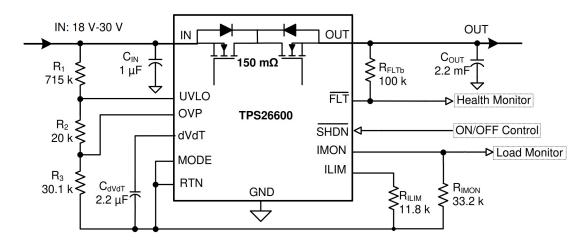

Zum Schutz der Hardware vor zu hohen Spannungen sowie Verpolung, wird auf dem Frequenzumrichter ein elektrischer Verpolungsschutz integriert. Dazu wird der TPS26601 von TI verwendet [26]. Dieser kompakte Integrated Circuit (IC) kombiniert mit wenigen externen passiven Komponenten die gewünschten Funktionen.

Gemäß der Schaltung in Abbildung 4.3, ist lediglich die Verwendung von zwei externen Spannungsteilern erforderlich, um die beiden Schwellspannungen für die Überspannung sowie für eine zusätzliche Unterspannung einzustellen.

Abbildung 4.3: Beispielbeschaltung des TPS26600 zum Über/Unterspannungsschutz inklusive Verpolungsschutz [26]

Der Eingangsspannungsbereich liegt im Bereich von  $4.2\,\mathrm{V}$  bis  $60\,\mathrm{V}$  und ist somit ausreichend, um die im Abschnitt 4.2.1 geforderten Spannungen oberhalb von  $12\,\mathrm{V}$  zu überwachen.

Die Überspannung wird dabei in Abhängigkeit der maximalen Eingangsspannung von 42 V am LT8609 Schaltregler definiert [17].

Der Verpolungsschutz gewährleistet laut Datenblatt einen Schutz bis -60 V.

Die Implementierung wird im Abschnitt 5.5 detailliert beschrieben.

#### 4.2.6 Leistungsstufe

Die Leistungsstufe wird als externe Komponente dazugekauft. Dieser soll laut Lastenheft über Anschlüsse an die zu entwickelnde Hardware angeschlossen werden können. Im Abschnitt 4.1 wurde bereits der DRV8300DIPW-EVM als Beispielapplikation ausgewählt [16].

Die Leistungsstufe ermöglicht einen Betrieb zwischen 6 V und 100 V sowie 30 A Ausgangsstrom. Es besitzt bereits integrierte Current Shunt Amplifier (CSA) innerhalb der 3 Halbbrücken, um die Phasenströme zunächst über die Shuntwiderstände zu messen, damit diese dann verstärkt gemessen werden können [16].

Der integrierte Gatetreiber ist ein DRV8300 von TI [27].

Der Vorteil an dieser Leistungsstufe ist die Möglichkeit externe Spannungsversorgungen nutzen zu können. Sowohl für den Gatetreiber als auch für den integrierten Temperatursensor. Dadurch wird es möglich, das in der Abbildung 4.1 erarbeitete Konzept zu implementieren. Dazu können die integrierten Schaltregler über das Entfernen von sogenannten 0-Ohm Widerständen außer Betrieb gesetzt werden. Die nötige Spannungsversorgung wird dann wie in Abbildung 4.1 über die zu entwickelnde Hardware erbracht.

Die Vorlage für die benötigten Anschlüsse liefert das sogenannte LAUNCHXL-F280049C von TI, da die Leistungsstufe ursprünglich für den Anschluss an dieses Evaluationskit konzipiert wurde [28].

In der Abbildung 4.4 wird die Leistungsstufe dargestellt.

Abbildung 4.4: Beispielbild der Leistungsstufe DRV8300DIPW-EVM [16]

In der Abbildung 4.4 ist zu sehen, dass die Anschlüsse an die Hardware über Stiftleisten realisiert wird. Weitere Anschlüsse an der Oberseite sind die Motorphasen, die Versorgungsspannung sowie ein Hall-Interface auf der rechten Seite.

Die Implementierung der Anschlüsse und damit der Leistungsstufe wird im Abschnitt 5.6 detailliert beschrieben.

## 5 Implementierung

In diesem Kapitel wird die während des Systementwurfs herausgearbeitete Lösungsarchitektur implementiert.

Dies umfasst die Dimensionierung der im Abschnitt 4.2 genannten Baugruppen sowie die Einarbeitung in den Schaltplan und das Layout.

Abschließend wird der vollständige Frequenzumrichter abgebildet.

Die Implementierung wird in folgender Reihenfolge beschrieben:

- Schaltregler

- Mikrocontroller

- $\bullet$  USB/UART-Schnittstelle

- Ethernet

- Verpolungsschutz/Überspannungsschutz

- Leistungsstufe/GPIOs

- Frequenzumrichter

Die Abbildung 5.1 stellt den verwendeten Lagenaufbau dar.

Dabei handelt sich um eine Leiterplatine mit 4 Lagen. Die äußeren Lagen führen die Leiterbahnen mit lokalen Powerflächen. Die inneren Lagen sind eine großflächige Masse und die benötigten Powerflächen zur Versorgung.

Der Lagenaufbau ist vom Hersteller EUROCIRCUITS vorgegeben und ist als DEFINED IMPEDANCE pool für impedanzgesteuerte Lagenaufbauten geeignet [29].

Abbildung 5.1: Verwendeter Lagenaufbau

### 5.1 Schaltregler

Da die Schaltregler für die Versorgung der 12 V und 3,3 V-Ebene identisch sind, wird auf die separate Darstellung beider Regler verzichtet. Die Dimensionierung des Schaltreglers für die 3,3 V-Ebene wird detailliert beschrieben. Die Vorgehensweise wird analog für die 12 V-Ebene angewendet.

Im Anschluss wird die Implementierung des Schaltreglers für die 1,2 V-Ebene dargestellt.

#### 5.1.1 Dimensionierung 3,3 V-Ebene

Die Ausgangsspannung wird über einen Spannungsteiler am FB-Pin eingestellt. Dazu werden die Widerstände  $R_{13}$  und  $R_{15}$  mit der Formel 5.1 berechnet [17].

$$R_{15} = \frac{R_{13}}{\left(\frac{V_{\text{OUT}}}{0.782 \text{ V}} - 1\right)} = \frac{100 \text{ k}\Omega}{\left(\frac{3.3 \text{ V}}{0.782 \text{ V}} - 1\right)} = 30,9 \text{ k}\Omega$$

(5.1)

Bei einem ausgewählten Widerstandswert von 100 k $\Omega$  für  $R_{13}$  ergibt sich für eine Ausgangsspannung von 3,3 V, für  $R_{15}$  ein Wert von 30,9 k $\Omega$ .

Die Schaltfrequenz wird als Kompromiss zwischen Effizienz, Bauteilgröße und Eingangsspannungsbereich, über den Widerstand  $R_{16}$  auf 2 MHz eingestellt [17].

Für die Annäherung an die benötigte Spule und damit der Induktivität wird die Formel 5.2 verwendet [17].

$$L = \frac{V_{\text{OUT}} + 0.25 \text{ V}}{f_{\text{SW}}} = \frac{3.3 \text{ V} + 0.25 \text{ V}}{2 \text{ MHz}} = 1,775 \text{ }\mu\text{H}$$

(5.2)

Aufgrund der Formel 5.2 und der Empfehlung im Datenblatt des Reglers, fällt die Wahl auf eine Spule von Coilcraft, mit einer Induktivität von 2,2 µH [30].

Die Eingangskapazität wird auf Empfehlung des Datenblatts für den LT8609 eine Kombination aus den Werten  $4,7\,\mu\text{F}$  für  $C_{12}$  und  $100\,\text{nF}$  für  $C_{13}$  [17].

Die Ausgangskapazität wird über die Formel 5.3 angenähert [17].

$$C_{\text{OUT}} = \frac{100}{V_{\text{OUT}} \cdot f_{\text{SW}}} = \frac{100}{3,3 \text{ V} \cdot 2 \text{ MHz}} = 15,15 \text{ }\mu\text{F}$$

(5.3)

Eingesetzt wird eine Kombination aus  $10\,\mu\text{F}$  für  $C_{14}$  und  $4,7\,\mu\text{F}$  für  $C_{15}$ .

#### 5.1.2 Schaltplan und Layout

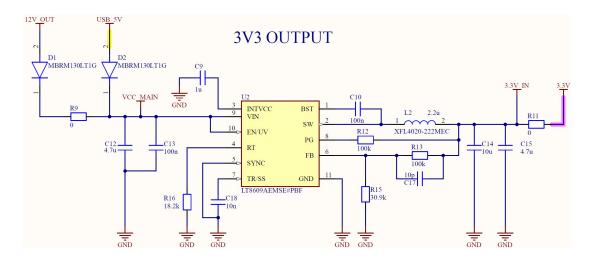

Die Beschaltung des Schaltreglers sowie die berechneten Parameter sind in der Abbildung 5.2 dargestellt.

Die Dioden  $D_1$  und  $D_2$  umfassen das im Abschnitt 4.2.1 benannte ORing-Verfahren [20].

Der Kondensator  $C_{18}$  wird im Datenblatt des Reglers empfohlen und soll einen Soft-Start ermöglichen, um hohen Strömen an der Versorgungsleitung entgegenzuwirken [17].

Weiterhin wird  $C_9$  empfohlen, um den internen Treiber zu regulieren [17].

Die Widerstände  $R_9$  und  $R_{11}$  sind eingefügt worden, um die schrittweise Verifizierung der Schaltregler zu ermöglichen. Weitere Informationen dazu sind im Abschnitt 6.1 beschrieben.

Alle weiteren Beschaltungen sind auf Empfehlung aus dem Datenblatt des LT8609 entnommen worden [17].

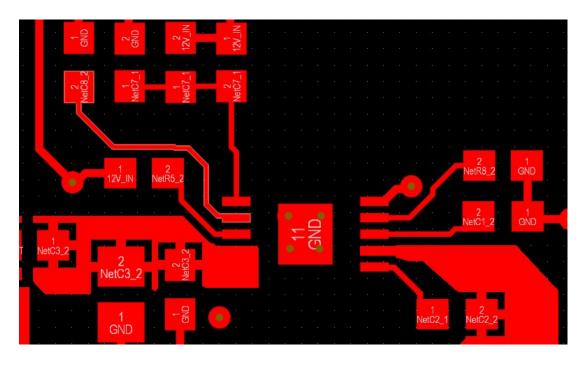

Das Layout ist auf der Abbildung 5.3 dargestellt. Die Empfehlungen in Bezug auf die Anordnung und das Verbinden der Bauteile wurden aus dem Datenblatt entnommen [17].

Abbildung 5.2: Schaltplan des LT8609-Reglers für die 3,3 V-Ebene

Abbildung 5.3: Layout des LT8609-Reglers für die 3,3 V-Ebene

#### 5.1.3 Dimensionierung 1,2 V-Ebene

Die Ausgangsspannung wird erneut über einen Spannungsteiler am FB-Pin eingestellt. Die Widerstandswerte werden über die Formel 5.4 berechnet [18].

$$R_{10} = R_{17} \cdot \left(\frac{V_{\text{OUT}}}{500 \text{ mV}} - 1\right) = 140 \text{ k}\Omega$$

(5.4)

Bei einem Widerstandswert von  $100 \,\mathrm{k}\Omega$  für  $R_{17}$ , ergibt sich bei einer Ausgangsspannung von  $1,2\,\mathrm{V}$  ein Wert von  $140 \,\mathrm{k}\Omega$  für  $R_{10}$ .

Die Schaltfrequenz beträgt erneut 2 MHz. Der LTC3302 wird mit einer festen Schaltfrequenz ausgeliefert und kann nicht über externe Bauelemente gesteuert werden [18].

Die Induktivität für die Spule wird über die Formel 5.5 angenähert [18].

$$L = \frac{V_{\text{OUT}}}{0.6 \text{ A} \cdot f_{\text{SW}}} \cdot \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN(MAX)}}}\right) = 636 \text{ nH}$$

(5.5)

Ausgewählt wird eine Spule von Murata mit einer Induktivität von 680 nH [31].

Die Ausgangskapazität wird über die Formel 5.6 angenähert.

$$C_{16} = 20 \cdot \frac{I_{\text{MAX}}}{f_{\text{SW}}} \cdot \sqrt{\frac{0,5}{V_{\text{OUT}}}} = 12,9 \mu \text{F}$$

(5.6)

Aufgrund der Empfehlung im Datenblatt des LTC3302 wird ein Kondensator mit 22 µF ausgewählt [18].

#### 5.1.4 Schaltplan und Layout

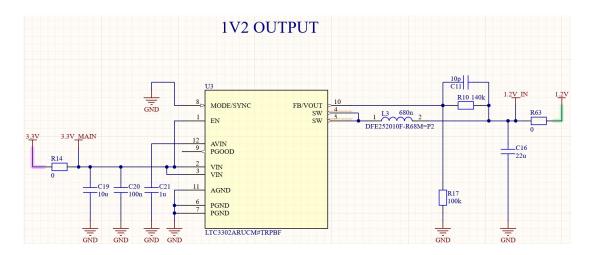

Der Schaltplan für den LTC3302 ist in der Abbildung 5.4 dargestellt.

Alle weiteren Beschaltungen sind auf Empfehlung aus dem Datenblatt des LTC3302 entnommen worden [18].

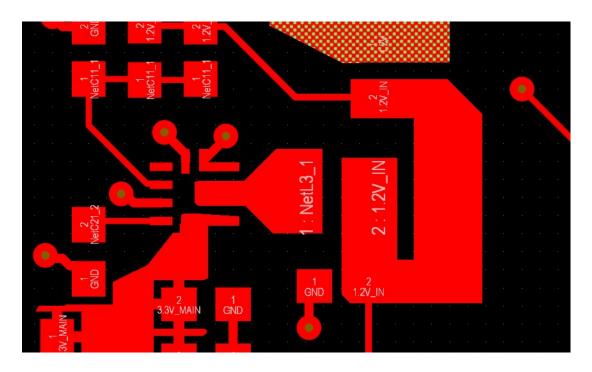

Das Layout ist in der Abbildung 5.5 dargestellt.

Die Anordnung ist erneut aus dem Datenblatt entnommen worden [18].

Abbildung 5.4: Schaltplan des LTC3302-Reglers für die 1,2 V-Ebene

Abbildung 5.5: Layout des LTC3302-Reglers für die 1,2 V-Ebene

## 5.2 Mikrocontroller

### 5.2.1 Schaltplan

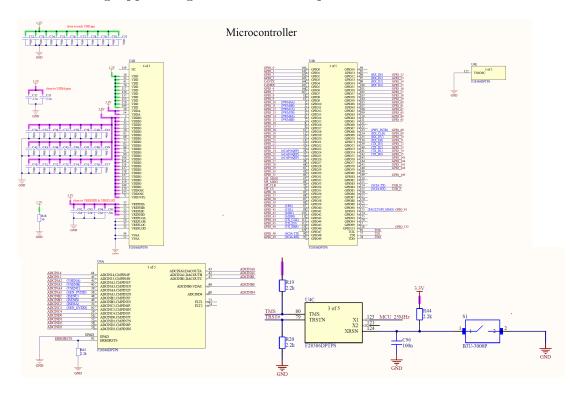

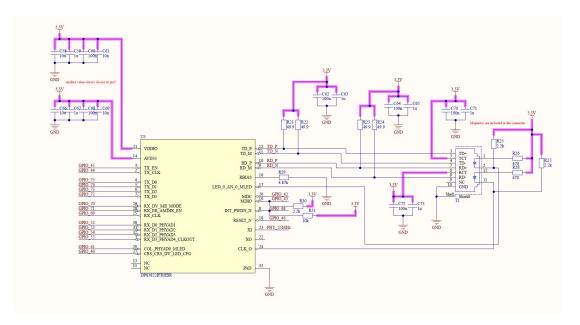

Der Schaltplan für den Mikrocontroller ist in der Abbildung 5.6 dargestellt. Um eine bessere Übersicht zu gewährleisten, wird der Mikrocontroller (U4) in einzelne Baugruppen aufgeteilt und dann separat beschrieben.

Abbildung 5.6: Schaltplan des Mikrocontrollers F28386D

#### • U4A:

Diese Baugruppe befindet sich unten links in der Abbildung.

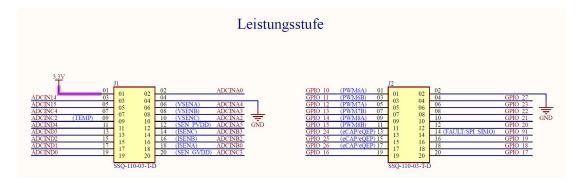

Hier befinden sich alle verfügbaren Analog/Digital-Converter (ADC) des Controllers sowie ein EPAD, der sich auf der Unterseite des F28386D befindet [8]. Alle verfügbaren ADCs werden auf die Stiftleisten geführt, um eine vollständige Nutzung dieser Funktion zu ermöglichen. Tatsächlich werden während dieser Arbeit aber nur die mit blauem Text versehenen ADCs genutzt, um die Leistungsstufe zu kontaktieren [4].

Zusätzlich sind zwei Flash Test (FLT) Pins verfügbar, diese werden hauptsächlich von TI genutzt und sind deshalb auf Empfehlung im Datenblatt des Mikrocontrollers nicht verbunden, sowie ein ERRORSTS-Pin [8].

#### • U4B:

Diese Baugruppe befindet sich oben rechts in der Abbildung.

Es umfasst alle verfügbaren General Purpose Input/Outputs (GPIOs) sowie einen Teil der Anschlüsse zum JTAG-Modul [8]. Neben den GPIOs, die verwendet werden, um einen Synchronmotor anzusteuern, wird der Großteil der GPIOs auf die verfügbaren Sitftleisten ausgeführt, um eine projektübergreifende Modularität zu gewährleisten

#### • U4C:

Diese Baugruppe befindet sich unten rechts in der Abbildung.

Neben den restlichen Pins, die für das JTAG-Modul benötigt werden, befindet sich hier ein Device-Reset Pin (XRSN) sowie die Anschlüsse für einen externen Quarz/Oszillator [8].

Die JTAG-Pins werden nach Vorgabe im Datenblatt angeschlossen [8]. Der XRSN-Pin verwendet einen externen Tastschalter, um den Mikrocontroller bei Betätigung zurücksetzen zu können [8, 32].

Ein externer Oszillator wird verwendet, da dieser eine bessere Frequenzstabilität gewährleistet und damit genauer ist als die verfügbaren internen Oszillatoren [33]. Auf Empfehlung im Datenblatt des F28386D, wird ein Oszillator mit einer Taktfrequenz von 25 MHz verwendet [8, 34].

#### • U4D:

die ADCs.

Diese Baugruppe befindet sich oben links in der Abbildung. In dieser Baugruppe befinden sich die Versorgungspins des Mikrocontrollers (VDDx,VSSA) sowie die Referenzspannungspins (VREFHx, VREFLx) für

Alle angeschlossenen passiven Bauelemente innerhalb dieser Baugruppe, wurden auf Empfehlung des Datenblatts für den Mikrocontroller verwendet [8].

#### • U4E:

Diese Baugruppe befindet sich oben rechts in der Abbildung.

Der VSSOSC-Pin ist die Masse-Referenz für den externen Oszillator und wird deshalb an dieselbe Masse-Referenz angeschlossen [8].

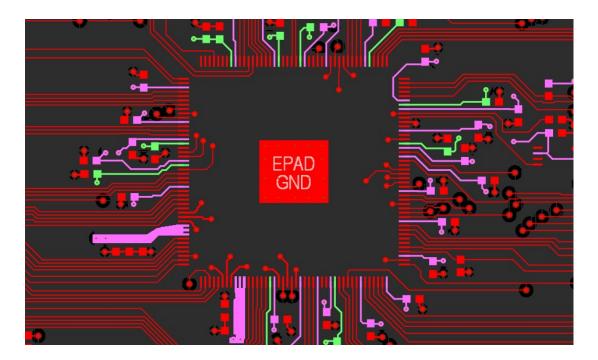

## 5.2.2 Layout

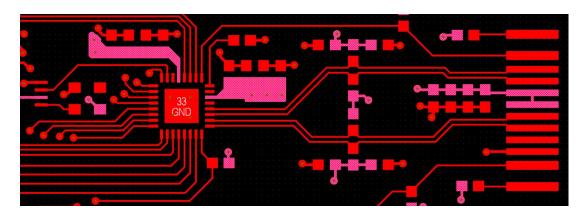

Das Layout des Mikrocontrollers ist in der Abbildung 5.7 dargestellt.

Der Mikrocontroller als zentraler Bestandteil der Hardware wird mittig auf der Platine implementiert. Alle weiteren Komponenten werden in der jeweiligen Umgebung der Pins positioniert. Dadurch wird die Implementierung der Komponenten vereinfacht, weil es zu geringeren Überschneidungen innerhalb der Signalleitungen führt.

Bei der Anordnung der Entkopplungskondensatoren wird besonders auf die Empfehlung im Datenblatt des Mikrocontrollers geachtet, um eine zuverlässige und funktionsfähige Anwendung zu ermöglichen [8].

Abbildung 5.7: Layout des Mikrocontrollers F28386D

## 5.3 USB/UART-Schnittstelle

#### 5.3.1 Schaltplan

Der FT2232HL ist wie im Abschnitt 4.2.3 beschrieben, als Kommunikationsschnittstelle sowie JTAG-Schnittstelle zuständig.

Der Anschluss wird über ein USB-C Buchse realisiert. Als USB-Standard wird USB 2.0 verwendet, da der FT2232HL keine weiteren Standards unterstützt [23, 35]. Zusätzlich bringt USB-C als verdrehsicherer, kompakter und moderner Stecker einen Vorteil im Vergleich zu seinen Vorgängern [35].

In der Abbildung 5.8 wird der Schaltplan des FT2232HL dargestellt.

Die Vorlage für die Versorgung des FT2232HL wird aus dem Datenblatt genommen. Dabei handelt es sich um eine sogenannte "Bus Powered"-Konfiguration [23]. Dabei wird die 5V vom USB Eingang über den LT8609-Schaltregler gespeist, um die benötigten 3,3 V für den FT2232HL zu gewährleisten. Zusätzlich wird der im Chip vorhandene 1,8 V Regler genutzt, um weitere im FT2232HL befindliche Peripherien zu versorgen.

Diese Art der Konfiguration wird bereits in der Abbildung 4.2 dargestellt.

Das Bauteil IC<sub>1</sub> ist ein Electro Static **Discharge** (ESD)-IC,um große elektrostatische Entladungen über den USB-Eingang abzuleiten und damit die Schaltung zu schützen [36, 37].

Zusätzlich benötigt der FT2232HL einen externen Electrically Erasable Programmable Read Only Memory (EEPROM), der für die gewünschte Programmierung des Chips zuständig ist [23]. Dadurch wird gewährleistet, dass die Ausgangsseitigen Kanäle am FT2232HL unterschiedlich programmiert werden können, um eine zusätzliche JTAG-Schnittstelle zu integrieren. Die Auswahl und Beschaltung des IC<sub>2</sub> wird aus dem Datenblatt des FT2232HL entnommen [23].

Weiterhin wird ein externer Quarz  $(Y_1)$  eingesetzt [38].

Abbildung 5.8: Schaltplan des USB/UART-ICs FT2232HL

Um die Genauigkeit des Quarzes sicherzustellen, muss die Lastkapazität angepasst werden [39]. Diese wird mit den Kondensatoren  $C_{88}$  und  $C_{89}$  realisiert.

Über die Formel 5.7 werden die Werte angenähert.

$$C_L = \frac{C_{88} \cdot C_{89}}{C_{88} + C_{89}} = 18 \text{ pF}$$

(5.7)

$C_L$  wird im Datenblatt des Quarzes mit 20 pF angegeben [38]. Es wird empfohlen auf die parasitären Kapazitäten innerhalb der Leitungen zu achten, daher wird zusätzlich ein Wert von 2 pF angenommen [39].

Zusätzlich wird über die Stiftleiste  $J_5$  die Möglichkeit eine externe JTAG-Schnittstelle zu nutzen, ermöglicht, um die Modularität zu erhöhen, falls der FT2232HL nicht genutzt wird.

### 5.3.2 Layout

In der Abbildung 5.9 wird das Layout des FT2232HL dargestellt.

Die Stiftleiste für die externe JTAG-Schnittstelle wird dabei so nah wie möglich am FT2232HL positioniert, um eine zuverlässige Funktion bei Anwendung zu gewährleisten. Dabei werden maximal Entfernungen von 15 cm empfohlen [8].

Die USB-Datenleitungen werden als differenzielle Signale implementiert, um Störeinflüsse zu vermindern [40]. Weiterhin wird eine Impedanz von  $90\,\Omega$  für die Leitungen empfohlen und eingesetzt [41].

Abbildung 5.9: Layout des USB/UART-ICs FT2232HL

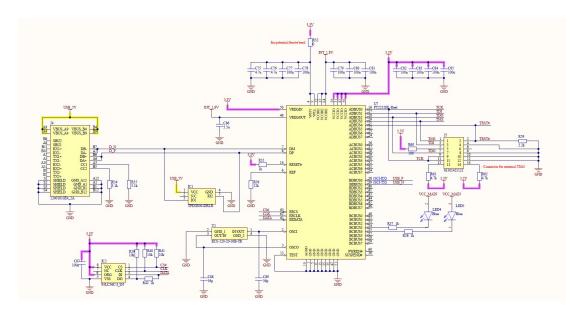

#### 5.4 Ethernet

#### 5.4.1 Schaltplan

Wie bereits im Abschnitt 4.2.4 beschrieben, wird die gleiche Ethernet-Schnittstelle wie auf der controlCARD TMDSCNCD28388D implementiert [24]. Dazu gehört auch die Implementierung des externen Oszillators, der bereits beim Mikrocontroller (Abschnitt 5.2) eingesetzt wurde. Der Ausgang am Oszillator wird dabei über einen Buffer jeweils an die Takteingänge von Mikrocontroller und Ethernet PHY geleitet [42].

Der Schaltplan der Ethernet-Schnittstelle ist in der Abbildung 5.10 dargestellt.

Abbildung 5.10: Schaltplan der Ethernet-Schnittstelle DP83822

Aufgrund der unterschiedlichen Gehäuseausführungen des hier verwendeten Mikrocontrollers im Vergleich zur controlCARD, welcher ein BGA-Gehäuse nutzt, erfordert dies eine Neuanpassung der Portanschlüsse. Das QFP-Gehäuse weist eine reduzierte Anzahl an verfügbaren GPIOs auf, wodurch die identischen Ports nicht verwendet werden können.

#### 5.4.2 Layout

Das Layout für die Ethernet-Schnittstelle ist in der Abbildung 5.11 dargestellt.

Beim Layout müssen besondere Regeln beachtet werden, um eine zuverlässige Signalintegrität zu gewährleisten. Hierbei wird besonders auf die Empfehlungen im Datenblatt des DP83822 geachtet [10].

Dazu gehört die Impedanzanpassung an den MII- und MDI-Leitungen. Diese umfassen folgende Ports [10]:

- MII:  $(50 \Omega \text{ single-ended})$

- $TX_D(0-3)$  Transmit Data

- TX CLK Transmit Clock

- RX D(0-3) Receive Data

- RX CLK Receive Clock

- MDI:  $(100 \Omega \text{ differential})$

- TD M & TD P Differential Transmit Output

- $\ensuremath{\mathtt{RD}}\xspace_{-}\ensuremath{\mathtt{M}}$ &  $\ensuremath{\mathtt{RD}}\xspace_{-}\ensuremath{\mathtt{P}}$  Differential Receive Output

Abbildung 5.11: Layout der Ethernet-Schnittstelle DP83822

Weiterhin werden an den MII-Leitungen maximale und relative Leitungslängen zueinander definiert. TI empfiehlt dabei maximale Leitungslängen von 15,24 cm sowie weitere 5,08 cm zwischen den einzelnen Leitungen [43].

## 5.5 Verpolungsschutz/Überspannungsschutz

#### 5.5.1 Dimensionierung

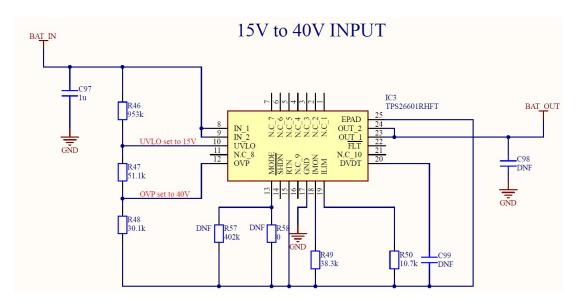

Zu Beginn wird der minimale und maximale Eingangsspannungsbereich definiert.

Minimal wird dabei ein Spannungswert benötigt, der groß genug ist, um die 12 V am Ausgang des LT8609 Schaltreglers zu gewährleisten. Hierbei wird eine Spannung von mindestens 15 V definiert.

Der maximale Spannungswert orientiert sich wie bereits im Abschnitt 4.2.5 angesprochen, an der maximal zulässigen Spannung am LT8609-Schaltregler. Hierbei wird ein maximaler Spannungswert von 40 V definiert. Damit wird eine Toleranz von 2 V zu der maximalen Eingangsspannung von 42 V am LT8609 gewährleistet.

Eine Übersicht über die Spannungsbereiche wird in der Abbildung 4.2 gegeben.

Die Spannungsgrenzen werden über die externen Widerstände  $R_{46}$ ,  $R_{47}$ ,  $R_{48}$  implementiert.

Die Werte für die Widerstände werden über die Formeln 5.8 und 5.9 berechnet [26].

$$V_{\text{OVPR}} = \frac{R_{48}}{R_{46} + R_{47} + R_{48}} \cdot V_{\text{OV}} \tag{5.8}$$

$$V_{\text{UVLOR}} = \frac{R_{47} + R_{48}}{R_{46} + R_{47} + R_{48}} \cdot V_{\text{UV}} \tag{5.9}$$

Die Werte für  $V_{\text{OVPR}}$  und  $V_{\text{UVLOR}}$  werden im Datenblatt mit 1,19 V vorgegeben [26]. Für  $R_{48}$  wird ein Wert von 30,1 k $\Omega$  bestimmt.

Dadurch ergibt sich für  $R_{47}$  ein Wert von 51,1 k $\Omega$  und für  $R_{46}$  ein Wert von 953 k $\Omega$ .

Ein maximaler Stromlimit wird über die Formel 5.10 eingestellt [26].

$$R_{50} = \frac{12}{I_{\text{LIM}}} = 10,7 \text{ k}\Omega \tag{5.10}$$

Mit einem Wert von  $10.7 \text{ k}\Omega$  für  $R_{50}$ , wird ein Stromlimit von 1.1 A implementiert.

#### 5.5.2 Schaltplan

Mit den berechneten Parametern ergibt sich die Beschaltung gemäß Abbildung 5.12.

Die Widerstände und Kondensatoren mit einem "DNF" gekennzeichnet, werden nicht auf der Platine bestückt und dienen als potentielle Stellschrauben, um gegebenenfalls zusätzliche Funktionen sowie gewünschte Schaltverhalten in die Schaltung zu implementieren [26].

Abbildung 5.12: Schaltplan der Überspannungsschaltung TPS26601

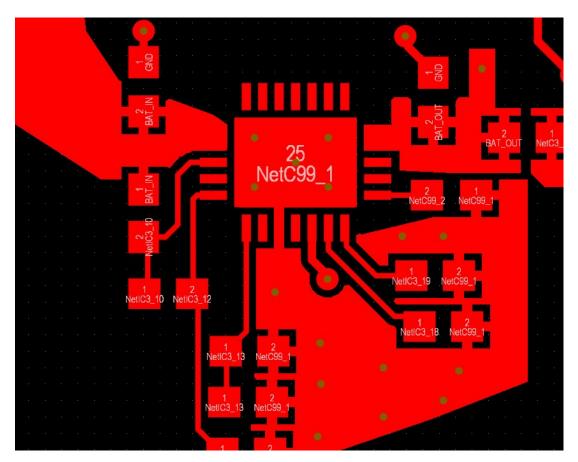

### 5.5.3 Layout

Um den Verpolschutz zu gewährleisten, wird drauf geachtet, dass der RTN-PIN am TPS26601 nicht an die Masse angeschlossen ist [26]. Zusätzlich wird empfohlen das PAD an der Unterseite vom Baustein TPS26601 an den RTN-Pin anzuschließen, um eine verbesserte Wärmeabführung zu ermöglichen [26].

Abbildung 5.13: Layout der Überspannungsschaltung TPS26601

## 5.6 Leistungsstufe/GPIOs

#### 5.6.1 Schaltplan

Die Anschlüsse für die Leistungsstufe werden, wie bereits im Abschnitt 4.2.6 beschrieben, gemäß des Hardware am LAUNCHXL-F280049C von TI implementiert [28].

Die Abbildung 5.14 stellt den Schaltplan für die Anschlüsse an die Leistungsstufe dar.

Es handelt sich um zwei 20-polige Steckerleisten, die entsprechend der Leistungsstufe an die Ports des Mikrocontrollers angeschlossen werden [16]. Die Ports mit den blauen Texten stellen hierbei den Kontakt zu der Leistungsstufe dar. Alle weiteren Ports werden gemäß des Lastenhefts (siehe Anhang A.1.1) an zusätzliche GPIOs sowie ADCs angeschlossen.

Abbildung 5.14: Schaltplan der Anschlüsse für die Leistungsstufe

Die Abbildung 5.15 stellt den Schaltplan für zusätzliche Anschlüsse am Mikrocontroller dar. Diese Anschlüsse werden erneut gemäß Lastenheft implementiert, um die Modularität des Frequenzumrichters zu gewährleisten. Dazu gehört die Implementierung von GPIOs, die eine weitere Ansteuerung einer Synchronmaschine mit Hallsensorik ermöglichen sowie einer zusätzlichen SPI-Schnittstelle, um den Umfang an Kommunikationsschnittstellen zu erhöhen.

Abbildung 5.15: Schaltplan der Anschlüsse für weitere GPIOs

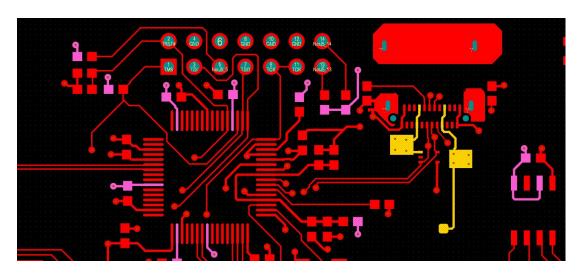

#### 5.6.2 Layout

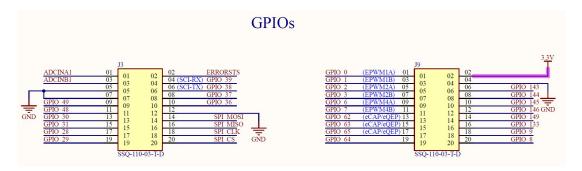

Die Abbildung 5.16 stellt das Layout für die Anschlüsse an die Leistungsstufe sowie weiterer GPIOs dar.

Die Anschlüsse links und rechts in der Abbildung werden genutzt um die Leistungsstufe zu kontaktieren.

Da das Layout der Signalleitungen, aufgrund von Signalkreuzungen, nicht auf einer Lage erfolgt, wird besonders auf die Anbindung an eine vollumfängliche Referenzlage geachtet.

Sogenannte Split-Planes können bei Nichtbeachtung zu ungewollten Kopplungen zwischen Leiterbahnen führen und damit die Signalqualität beeinträchtigten [7].

Für die Signale auf der ersten Lage, dient die Massefläche auf der Lage 2 als Referenz, während für die Signalleitungen auf der Lage 4 die Powerfläche auf der Lage 3  $(3,3\,\mathrm{V})$  als Referenz dient.

Abbildung 5.16: Layout der Anschlüsse für die Leistungsstufe

## 5.7 Frequenzumrichter

Den Abschluss der Implementierung stellt die in Abbildung 5.17 dargestellte, entwickelte Hardware ohne Leistungsstufe dar.

Der Anschluss zum 12 V-Regler wird über eine Leiterplattenklemme vom Unternehmen WAGO realisiert [44]. Siehe links im Bild.

Am unteren Rand der Hardware befinden sich zusätzliche User-LEDs, die genutzt werden können, um Statusanzeigen abzubilden.

Das CAN-Interface befindet sich am oberen Rand der Hardware und wird über ein Klemmblock von PHOENIX CONTACT angesteuert [45].

Die Verifikation und Inbetriebnahme der Hardware erfolgt im nächsten Kapitel.

Abbildung 5.17: Entwickelte Hardware ohne Leistungsstufe

# 6 Verifikation

Dieser Kapitel beschreibt den Verifikationsprozess der entwickelten Hardware. Die Verifikation erfolgt gemäß dem Verifikationsplan im Lastenheft (siehe Anhang A.1.1).

Zu Beginn erfolgen die Tests der Versorgungspfade. Dazu gehört die Verifikation des Über- und Unterspannungsschutzes sowie die Inbetriebnahme der Schaltregler.

Im nächsten Schritt werden die weiteren Module verifiziert. Dies beinhaltet die Kommunikation zum Mikrocontroller sowie Ethernet-PHY. Anschließend wird der Anschluss zur Leistungsstufe überprüft, um die gewünschte Kontaktierung zur Hardware zu verifizieren.

Die Verifikationen in Bezug auf das Gesamtsystem, sind in der parallel verfassten Masterarbeit von Baris Akgül im Detail beschrieben [4].

## 6.1 Versorgungspfad

Zu Beginn wird die Baugruppe für den Über- und Unterspannungsschutz verifiziert. Während der Inbetriebnahme werden alle im Anschluss befindlichen Baugruppen über das Entfernen von  $0\,\Omega$ -Widerständen an den Schaltreglern (siehe Abschnitt 5.1) außer Betrieb genommen. Durch diese Maßnahme wird sichergestellt, dass die Baugruppen schrittweise verifiziert werden können, um potentiellen Schaden an Bauteilen abzuwenden.

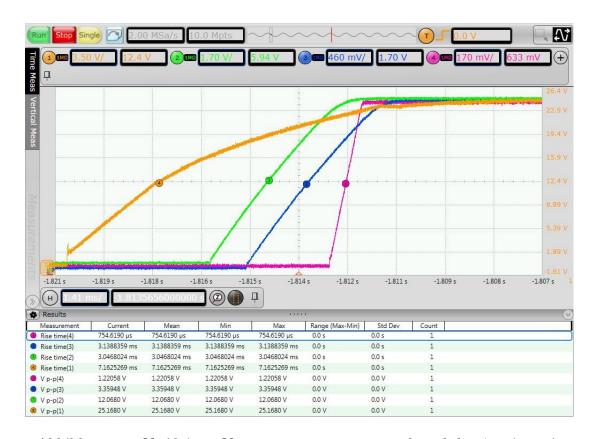

Die Versorgungsspannung wird sowohl am Eingang als auch am Ausgang des TPS26601 gemessen und über den kompletten Spannungsbereich bis 42 V aufgezeichnet. Das Ergebnis ist auf der Abbildung 6.1 dargestellt. Der grüne Spannungsverlauf (Kanal 2) stellt den Eingang und der Spannungsverlauf in Gelb (Kanal 1) den Ausgang der Schaltung dar. Der Ausgang wird ab 15,25 V eingeschaltet und ab 40,34 V ausgeschaltet.

Abbildung 6.1: Verifizierter Über- sowie Unterspannungsschutz am TPS26601

Im nächsten Schritt werden die Schaltregler schrittweise angeschlossen und verifiziert. Die Tabelle 6.1 stellt die gemessenen Spannungswerte am Ausgang der Schaltregler dar.

| Spannungsebene     | gemessene<br>Spannung | geforderte<br>Spannung | Toleranz    |

|--------------------|-----------------------|------------------------|-------------|

| >12 V              | 25,16  V              | 25 V                   | 0,64 %      |

| 12 V-Schaltregler  | 12,06  V              | 12 V                   | 0,5 %       |

| 3,3 V-Schaltregler | 3,36  V               | 3.3  V                 | 1,8 %       |

| 1,2 V-Schaltregler | 1,22 V                | 1,2 V                  | $1,\!66~\%$ |

Tabelle 6.1: Gemessene Spannungsebenen mit Toleranzabweichungen

Der Effektivwert der Ausgangsspannung am 3,3 V-Schaltregler mit 3,36 V hat dabei die größte Abweichung von 1,8% am Ausgang der Schaltregler. Diese Toleranz befindet sich innerhalb der Simulationsergebnisse von Sigrity PowerDC genutzten Anforderungen von maximal 2% und wird deshalb freigegeben [46]. Die Simulationsergebnisse sind zusätzlich im Anhang hinzugefügt (siehe Anhang A.1.9 und A.1.10).

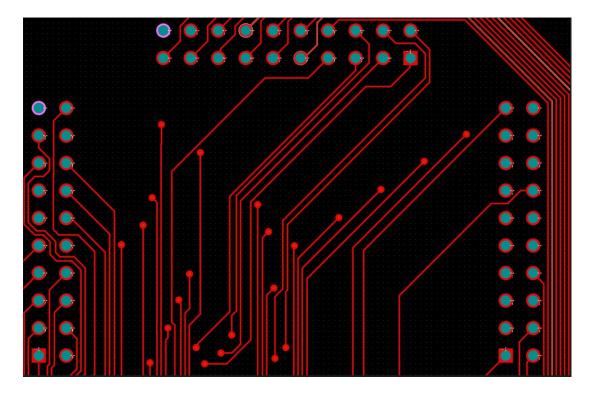

Mit der Verifikation der gemessenen Spannungen, wird zudem das Einschaltverhalten der einzelnen Schaltregler analysiert. Dazu wird ein Oszilloskop mit vier Kanälen genutzt, um die Eingangsspannung sowie die Anstiegsrampen der Spannungsebenen zu visualisieren. Die Ergebnisse werden in der Abbildung 6.2 dargestellt.

Die Formel 6.1 gibt zudem eine Näherung an die Anstiegszeit der Ausgangsspannungen am LT8609 dar [17, 47].

$$T_{SS} = C_{SS} \cdot \frac{V_{SS/TR(MAX)}}{I_{SS}} = 4 \text{ ms}$$

$$(6.1)$$

Gemäß dem Kondensator am TR/SS-Pin wird eine maximale Anstiegszeit von 4 ms am Ausgang der 12 V und 3,3 V-Ebene erwartet. Die gemessenen Verläufe in der Abbildung 6.2 zeigen, dass die Ausgangsspannungen ihren Sollwert innerhalb eines Zeitraums von ca. 3,04 ms bis 3,14 ms erreichen. Diese Werte befinden sich innerhalb der in Formel 6.1 berechneten maximalen Anstiegszeit und werden deshalb verifiziert.

Die Soft-Start Anstiegszeit am LTC3302 für die 1,2 V-Ebene wird im Datenblatt mit maximal 3 ms angegeben [18]. Der gemessene Wert beträgt ca. 0,75 ms bis es seinen Sollwert erreicht und entspricht somit der Anforderung und wird verifiziert.

Abbildung 6.2: Verifizierte Versorgungsspannungen während der Anstiegszeit

## 6.2 Kommunikationspfad: Mikrocontroller

Zunächst wird die Kommunikation zum Mikrocontroller analysiert. Zu Beginn wird der FT2232HL von FTDI programmiert, um die Schnittstelle zum Mikrocontroller herzustellen. Die Programmierung wird über die hauseigene Software von FTDI durchgeführt. Eine genaue Anleitung dazu ist vorgegeben [23].

Im nächsten Schritt wird die von TI bereitgestellte Entwicklungsumgebung (Code Composer Studio) genutzt, um eine Testverbindung zum Mikrocontroller herzustellen [48].

Zu Beginn war die Testverbindung nicht möglich, da die Beschaltung des FT2232HL nicht vollständig war. Der Schaltplan im Abschnitt 5.3 wurde mit zwei zusätzlichen Widerständen ergänzt. Diese Modifikation hat die erfolgreiche Verifikation der Testverbindung ermöglicht.

Die nachträglichen Änderungen an der Hardware sind dokumentiert und befinden sich in Form eines Erattas im Anhang (siehe Anhang A.1.8)

In der Abbildung 6.3 wird das Ergebnis einer erfolgreichen Testverbindung zum Mikrocontroller dargestellt.

Zum Testen wird der im Abschnitt 5.3 besprochene und implementierte JTAG-Standard genutzt.

```

Do a test using OXFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using OXO1FCIFID.

Scan tests: 4, skipped: 0, failed: 0

Do a test using OX5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using OXAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG IR Integrity scan-test has succeeded.

-----[Perform the Integrity scan-test on the JTAG DR]------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using OXFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using OXO0000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using OXFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using OXO1FC1FID.

Scan tests: 4, skipped: 0, failed: 0

Do a test using OXS533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using OXAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG DR Integrity scan-test has succeeded.

[End]

```

Abbildung 6.3: Verifikation der erfolgreichen Testverbindung zum Mikrocontroller

Da die Kommunikation zum Mikrocontroller verifiziert ist, wird auf die Verifikation der einzelnen Funktionen am Mikrocontroller verzichtet, da die in der Masterarbeit von Baris Akgül vorgestellte Simulink-Software eine Bestätigung der Funktionalität sicherstellt.

Diese Verifikationen in Bezug auf das Gesamtsystem sind in der Masterarbeit von Baris Akgül dokumentiert [4].

Weiterhin wird das Register vom Mikrocontroller modifiziert, um das Hochfahren des Mikrocontrollers über den FLASH-Speicher zu ermöglichen (Boot Mode). Das gewährleistet eine dauerhafte Einbindung der Software ohne den Verlust der Informationen nach einer Unterbrechung im Versorgungspfad [49].

Die Änderungen am Register sind dokumentiert und können im Anhang nachgeschaut werden (siehe Anhang A.1.8)

## 6.3 Kommunikationspfad: Ethernet

Als nächstes wird die Kommunikation zum Ethernet-PHY analysiert. Zu Beginn wird die Schnittstelle zwischen dem Mikrocontroller und der PHY verifiziert. Dazu werden die von TI bereitgestellten Beispielapplikationen innerhalb der Entwicklungsumgebung (Code Composer Studio) genutzt. Dazu stellt TI eine Bibliothek (C2000WARE) aus Software und Dokumentationen bereit [50].

Innerhalb dieser Bibliothek werden die internen Register des DP83822-PHYs über die Serial Management Interface (SMI)-Schnittstelle ausgelesen [10]. Diese Schnittstelle besteht aus zwei Leitungen, die sich innerhalb der Schaltung im Abschnitt 5.4 befinden. Der Port MDIO sorgt für den Datenaustausch während der MDC Port die Taktleitung ist [10].

Der genaue Protokollablauf ist im Datenblatt des DP83822 angegeben und kann dort nachgeschaut werden [10].

Das im DP83822 befindliche Register **B**asic **M**ode **C**ontrol **R**egister (BMCR) ermöglicht über die Änderung des Bits (14) den sogenannten MII Loopback, um die Kommunikation zwischen MAC und der PHY zu verifizieren [10].

Die Tabelle 6.2 zeigt die Adresse des Registers BMCR sowie die standardmäßige Reihenfolge der Bits in Binärform.

| $\mathbf{Adresse}$ | $\operatorname{Bits}$ |

|--------------------|-----------------------|

| 0x0000             | 0111000100000000      |

Tabelle 6.2: Verifizierte BMCR-Registeradresse mit standardmäßiger Bitreihenfolge

Der Verifikationsprozess in Bezug auf das Gesamtsystem ist in der Masterarbeit von Baris Akgül dokumentiert [4].

## 6.4 Integrationstest: Frequenzumrichter

Abschließend wird in diesem Abschnitt das Zusammenwirken der entwickelten Hardware und der Leistungsstufe verifiziert. Dazu gehört die Verifikation der ordnungsgemäßen Kontaktierung über die implementierten Anschlüsse sowie die Versorgung der Leistungsstufe durch diese.

Die Abbildung 6.4 zeigt den zusammengebauten Frequenzumrichter samt angeschlossenem Motor.

Abbildung 6.4: Fertiggestellter Frequenzumrichter mit angeschlossenem Motor

Die Phasenanschlüsse sowie die Leitungen für den Hallgeber werden direkt über die Leistungsstufe angeschlossen. Die Leistungsstufe selber wird über die im Abschnitt 5.6 implementierten Stiftleisten kontaktiert.

Die Versorgung der Leistungsstufe und somit des Gatetreibers innerhalb der 12 V-Ebene (GVDD) wird durch die LEDs auf der Leistungsstufe überprüft [16].

Zur Verifikation des gesamten Frequenzumrichters wird die Funktion im System innerhalb der Masterarbeit von Baris Akgül getestet [4].

# 7 Fazit und Ausblick

Das Ziel dieses Projekts, einen modularen Frequenzumrichter zu entwickeln, konnte durch das methodische Vorgehen mit Hilfe der CONSENS®-Methode umgesetzt werden.

Die Ausarbeitung der Anforderungserhebung als Grundlage der Entwicklung einer Systemarchitektur hat den Prozess des Systementwurfs zudem beschleunigt, um die Qualität in der Implementierung sicherzustellen.

Der modulare Frequenzumrichter konnte mit der parallel entwickelten modellbasierten Software innerhalb eines Gesamtsystems unter Hinzunahme einer Synchronmaschine integriert und erprobt werden. Dadurch wurde die erarbeitete Systemarchitektur sowie kritische Systemelemente identifiziert, um eine solide Grundlage für weitere Optimierungsmaßnahmen zu schaffen.

Für künftige Arbeiten bietet sich die Möglichkeit, den Frequenzumrichter durch die Integration einer selbstentwickelten Leistungsstufe weiter zu optimieren. Zusätzlich kann die Definition weiterer Anforderungen genutzt werden, um die Baugröße des Frequenzumrichters zu reduzieren. Des Weiteren bietet sich die Anwendung der Anforderungserhebung als Grundlage an, um eine Integration des Frequenzumrichters in die Beispielapplikation Cargo-Pedelec zu ermöglichen.

Den Abschluss dieses Projektes stellt ein funktionsfähiger Frequenzumrichter für die Ansteuerung von einer Synchronmaschine dar.

# Abbildungsverzeichnis

| 2.1 | QFP-Gehäuse [5]                                                                     | 4  |

|-----|-------------------------------------------------------------------------------------|----|

| 2.2 | Beispielhafte Anwendung einer differenziellen Signalübertragung [11]                | 5  |

| 2.3 | Beispielhafte Leitungsgeometrien für Signalimpedanzen an single-                    |    |

|     | ended und differenziellen Signalen [6]                                              | 6  |

| 3.1 | Umfeldmodell Cargo-Pedelec                                                          | 8  |

| 3.2 | Wirkstruktur Elektronik                                                             | 10 |

| 3.3 | Wirkstruktur Motorcontroller/Frequenzumrichter                                      | 11 |

| 3.4 | Komponenten des Motorcontrollers und die dazugehörigen Span-                        |    |

|     | nungsebenen                                                                         | 12 |

| 3.5 | Blockschaltbild Gesamtsystem                                                        | 13 |

| 4.1 | Vergleich der Konzepte zur Versorgung des Frequenzumrichters                        | 16 |

| 4.2 | Eingangs- und Ausgangsströme der Schaltregler und Verbraucher                       | 19 |

| 4.3 | Beispielbeschaltung des TPS26600 zum $\ddot{\mathrm{U}}\mathrm{ber/Unterspannungs}$ |    |

|     | schutz inklusive Verpolungsschutz [26]                                              | 22 |

| 4.4 | Beispielbild der Leistungsstufe DRV8300DIPW-EVM [16]                                | 24 |

| 5.1 | Verwendeter Lagenaufbau                                                             | 26 |

| 5.2 | Schaltplan des LT8609-Reglers für die 3,3 V-Ebene                                   | 29 |

| 5.3 | Layout des LT8609-Reglers für die 3,3 V-Ebene $\ \ldots \ \ldots \ \ldots$          | 29 |

| 5.4 | Schaltplan des LTC3302-Reglers für die 1,2 V-Ebene                                  | 31 |

| 5.5 | Layout des LTC3302-Reglers für die 1,2 V-Ebene                                      | 31 |

| 5.6 | Schaltplan des Mikrocontrollers F28386D                                             | 32 |

| 5.7 | Layout des Mikrocontrollers F28386D                                                 | 35 |

| 5.8 | Schaltplan des USB/UART-ICs FT2232HL                                                | 37 |

| 5.9 | Layout des USB/UART-ICs FT2232HL                                                    | 38 |

## Abbildungs verzeichn is

| 5.10 | Schaltplan der Ethernet-Schnittstelle DP83822                     | 39 |

|------|-------------------------------------------------------------------|----|

| 5.11 | Layout der Ethernet-Schnittstelle DP83822                         | 40 |

| 5.12 | Schaltplan der Überspannungsschaltung TPS26601                    | 42 |

| 5.13 | Layout der Überspannungsschaltung TPS26601                        | 43 |

| 5.14 | Schaltplan der Anschlüsse für die Leistungsstufe                  | 44 |

| 5.15 | Schaltplan der Anschlüsse für weitere GPIOs                       | 45 |

| 5.16 | Layout der Anschlüsse für die Leistungsstufe                      | 46 |

| 5.17 | Entwickelte Hardware ohne Leistungsstufe                          | 47 |

|      |                                                                   |    |

| 6.1  | Verifizierter Über- sowie Unterspannungsschutz am TPS26601        | 49 |

| 6.2  | Verifizierte Versorgungsspannungen während der Anstiegszeit       | 51 |

| 6.3  | Verifikation der erfolgreichen Testverbindung zum Mikrocontroller | 53 |

| 6.4  | Fertiggestellter Frequenzumrichter mit angeschlossenem Motor      | 55 |

# **Tabellenverzeichnis**

| 4.1 | Parameter mit möglichen Lösungsarchitekturen und gewählte Lösung | 14 |

|-----|------------------------------------------------------------------|----|

| 3.1 | Gemessene Spannungsebenen mit Toleranzabweichungen               | 50 |

| 3.2 | Verifizierte BMCR-Registeradresse mit standardmäßiger Bitrei-    |    |

|     | henfolge                                                         | 54 |

# Literatur

- [1] Raphael-David Volmering. »Entwicklung der Leistungselektronik eines E-Skateboards«. Masterthesis. Hochschule Bochum Bochum University of Applied Sciences, 2015.

- [2] Sean William Dalton. »Entwicklung der eingebetteten Hardware einer modularen Antriebsplattform«. Bachelorthesis. Hochschule Bochum Bochum University of Applied Sciences, 2017.

- [3] Enes Darici Baris Akgül. »Planung und Konzeption eines modularen Frequenzumrichters«. Entwicklungsprojekt. Hochschule Bochum Bochum University of Applied Sciences, 2023.

- [4] Baris Akgül. »Modellbasierte Entwicklung und Verifikation mit MATLAB/-Simulink eines modularen Frequenzumrichters«. Masterthesis. Hochschule Bochum Bochum University of Applied Sciences, 2023.

- [5] Analog Devices. Power Bypass Decoupling of SHARC® Processors. EE-253, 2006.

- [6] Toradex. Layout Design Guide. V1.0, 2015.

- [7] Martin Graham Howard Johnson. *HIGH-SPEED DIGITAL DESIGN*. A HANDBOOK OF BLACK MAGIC, 1993.

- [8] Texas Instruments. TMS320F2838x Real-Time Microcontrollers With Connectivity Manager. SPRSP14E, 2023.

- [9] A Ciccomancini Scogna, A Orlandi und V Ricchiuti. »Signal integrity analysis of single-ended and differential signaling in PCBs with EBG structure«. In: 2008 IEEE International Symposium on Electromagnetic Compatibility. IEEE. 2008, S. 1–6.

- [10] Texas Instruments. DP83822 Robust, Low Power 10/100 Mbps Ethernet Physical Layer Transceiver. SNLS505G, 2023.

- [11] Texas Instruments. High-Speed Interface Layout Guidelines. SPRAAR7J, 2023.

- [12] Smart Mechatronics GmbH. CONSENS. Workshop HS Bochum, 2016.

- [13] Florian Wagner. »Modellbasierte Entwicklung und Verifikation einer modularen Antriebsplattform mit MATLAB/Simulink«. Masterthesis. Hochschule Bochum Bochum University of Applied Sciences, 2017.

- [14] Lea Deutscher. Ȇbersicht | Pedalsensoren «. In: https://windmeile. com/pedalsensoren ().

- [15] Fabian Billing Christian Schawel. Top 100 Management Tools. pp 174-176, 2012.

- [16] Texas Instruments. DRV8300xxx-EVM User's Guide. SLVUBV6, 2020.

- [17] Analog Devices. Synchronous Step-Down Regulator with 2.5 A Quiescent Current42V, 3A Synchronous Step-Down Regulator with 2.5µA Quiescent Current. https://www.analog.com/media/en/technical-documentation/data-sheets/lt8609-8609a-8609b.pdf, 2021.

- [18] Analog Devices. 5V, 2A Synchronous Step-Down Regulator in  $2mm \times 2mm$  FCQFN. https://www.analog.com/media/en/technical-documentation/data-sheets/ltc3302.pdf, 2023.

- [19] Joachim Specovius. *Grundkurs Leistungselektronik*. Bd. 10. Auflage. Springer Vieweg, 2020.

- [20] Martin Patoka. »Fundamentals of power system ORing. 2007. [Electronic resource] «. In: https://www.eetimes.com/fundamentals-of-power-system-oring/[in English] ().

- [21] The MathWorks. Host-Target Communication with External Mode Simulation. https://de.mathworks.com/help/ecoder/armcortexa/ug/set-up-and-use-hosttarget-communication-channel.html, 2023.

- [22] The MathWorks. What Is Hardware-in-the-Loop (HIL)? https://nl.mathworks.com/discovery/hardware-in-the-loop-hil.html, 2023.

- [23] Future Technology Devices International Ltd. FT2232H Dual High Speed USB to Multipurpose UART/FIFO IC.  $FT_000061$ , 2023.

- [24] Texas Instruments. TMS320F28388D controlCARD Information Guide. SPRUIL8B, 2020.

- [25] Stephan Günther. JTAG-Interface. https://tu-dresden.de/ing/informatik/ti/vlsi/ressourcen/dateien/dateien\_studium/dateien\_lehstuhlseminar/vortraege\_lehrstuhlseminar/hs\_ws\_0708/jtag-schnittstelle.pdf?lang=de, 2023.

- [26] Texas Instruments. TPS2660x 60-V, 2-A Industrial eFuse With Integrated Reverse Input Polarity Protection. SLVSDG2G, 2019.

- [27] Texas Instruments. DRV8300: 100-V Three-Phase BLDC Gate Driver. SLVSFG5D, 2022.

- [28] Texas Instruments.  $C2000^{\text{TM}} \ Piccolo^{\text{TM}} \ F28004x \ Series \ LaunchPad^{\text{TM}} \ Development \ Kit. SPRUII7B, 2020.$

- [29] Eurocircuits. PCB Configurator DEFINED IMPEDANCE pool.., 2019.

- [30] Coilcraft. Shielded Power Inductors XFL4020. 745-1, 2021.

- [31] Murata Electronics. Reference Specifications DFE252010F. J(E)TE243A-0012B-01, 2023.

- [32] Omron Electronics. *Ultra-small Tactile Switch (SMT) B3U.* A162-E1-07, 2018.

- [33] Mark Harris. »Wie wichtig ist Ihre Mikrocontroller-Taktquelle?. 2021. [Electronic resource] «. In: https://resources.altium.com/de/p/how-important-your-microcontroller-clock-source-0#data-sampling ().

- [34] ECS INC. ECS-2520S SMD CRYSTAL OSCILLATOR. https://www.mouser.de/datasheet/2/122/ECS\_2520S-1064133.pdf, 2020.

- [35] Robert Murphy. USB 101: An Introduction to Universal Serial Bus 2.0. AN57294, 2017.

- [36] EOS/ESD Association; Inc.; Rome; NY. Fundamentals of Electrostatic Discharge. Part One, 2020.

- [37] Texas Instruments. TPD2E001 Low-Capacitance 2-Channel ESD-Protection for High-Speed Data Interfaces. SLLS684I, 2016.

- [38] ECS International. ECX-53B SMD CRYSTAL. 2017.

- [39] Texas Instruments. AN100 Crystal Selection Guide. SWRA372C, 2013.

- [40] Douglas Brooks. Differential Signals Rules to Live By. 2001.

- [41] Silicon Labs. USB Hardware Design Guidelines. AN0046, 2020.

- [42] Texas Instruments. CDCLVC11xx 3.3-V and 2.5-V LVCMOS High-Performance Clock Buffer Family. SCAS895B, 2017.

- [43] Texas Instruments. AN-1469 PHYTER Design Layout Guide. SNLA079D, 2013.

- [44] Wago. THR PCB terminal block; push button. https://www.farnell.com/datasheets/2856539.pdf, 2019.

- [45] Phoenix Contact. PCB terminal block PTS 1,5/5-5,0-H 1792892. https://datasheet.datasheetarchive.com/originals/dk/DKDS-4/68933.pdf, 2012.

- [46] cadence. Sigrity PowerDC. DC, thermal analysis for packages und boards, 2017.

- [47] Texas Instruments. Sequencing and Tracking With the TPS621-Family and TPS821-Family. SLVA470A, 2017.

- [48] Texas Instruments.  $C2000^{\text{TM}}$  Software Guide. 2023.

- [49] Texas Instruments. TMS320F28x Boot Features and Configurations. SPRA-CA2A, 2022.

- [50] Texas Instruments. C2000Ware Quick Start Guide. SPRUI46D, 2019.

# A Anhang

## A.1 Inhalt

- ${\bf 1} \ \ Dokumente \setminus Lastenheft \_Motorcontroller.pdf$

- ${\bf 2}\ \, {\rm Dokumente} \backslash {\rm Lastenheft\_CarPediem.pdf}$

- ${\bf 3}\ \ {\rm Dokumente} \backslash {\rm Anwendungs szenarien.pdf}$

- ${\bf 4}\ \ Dokumente \backslash Meilenstein plan.xlsx$

- ${\bf 5}\ \, {\rm Dokumente}\backslash {\rm BOM.csv}$

- ${\bf 6} \;\; {\rm Dokumente} \backslash {\rm HW\_Architektur\_Erfassung.xlsx}$

- ${\bf 7}\ \ {\bf Dokumente} \backslash {\bf CarPediem\_Motorcontroller\_schematic.pdf}$

- 8 Dokumente\Erratas.xlsx

- 9 reports\5V\_Simulation.htm

- ${\bf 10} \;\; {\bf reports} \backslash {\bf 36V\_Simulation.htm}$